- 03/30

- 2022

-

QQ扫一扫

-

Vision小助手

(CMVU)

背景和引言

随着卫星运营商在轨获取的数据越来越多,他们更愿意在载荷上处理这些数据并提取有价值的信息,而不是将大量数据下行传送到地面的云上进行后处理。现有宇航级半导体技术和/或射频带宽限制了可实时处理的数据量。我知道一些客户由于下行链路的需求违反了ITU的规定,而不得不降低他们的项目预期。 另一方面,尽可能接近原始数据源(即边缘)的局部处理基于对来自多个传感器的大量信息的实时计算,可通过使用低延迟的确定性接口和满足特定散热和可靠性要求的小型低功耗形状因数实现。在轨提取分析显著减少了延迟和RF下行带宽 – 我们正有效地将数据中心移动到原始数据的源头! 在这篇文章中,我想探讨和比较用于边缘密集型星载处理的微处理器和FPGA。一些应用需要从不同带宽的多个传感器(如RF、LIDAR、成像和GNSS)获取大量数据,同时需要实时做出关键决策,如用于航天器态势感知的物体识别和分类(即敌我识别)、避免空间碎片碰撞、高清视频地球观测、空间原位探测和资源利用等。利用机器学习技术在轨提取分析的自主星载处理的应用也呈上升趋势。

现有解决方案和局限性

目前的星载处理基于微处理器或FPGA,而这两种方案都没有对目标的人工智能的在轨特征进行优化。前者有利于控制、复杂决策并支持操作系统,后者可以处理各种高计算要求的算法,擅长数据传输、自定义加速、面向位的函数和接口。然而,现有解决方案不能有效地处理线性代数、矩阵或矢量处理,也不能利用低功耗的并行性来进行自主机器学习、人工智能推理以及用于特征检测和分类的神经网络实现。

在商业领域,最初为游戏玩家开发的GPU,正被用于加速加密、金融建模、网络和人工智能等众多计算任务。GPU 使用多核和并行处理来同时执行数千个线程,运行速度比微处理器更快,更具成本效益,能够对来自多个传感器的密集型数据进行分析计算,时间为毫秒级,而不是秒、分钟或小时。GPU经过优化,可以基于大量的存储信息快速地执行相同的操作,而CPU则倾向于经常跳转。

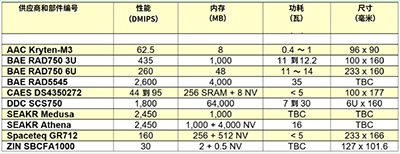

尽管市面上有接近30款宇航级微控制器、微处理器、FPGA和专用DSP引擎,但其中只有一小部分可以用于在轨边缘应用。许多现有设备没有足够的计算能力或低延迟的内存/I/O接口。有些会消耗太多电力,需要庞大而昂贵的散热管理解决方案。之前我探讨过如何保证宇航级半导体的良好散热,以确保其安全运行和最大限度的可靠性。表1列出了我考虑过的传统标准处理产品。对于下面列出的FPGA,标出的性能值是基于资源数和时钟频率的理论峰值。标准的V5QV不包含微处理器IP。

表1 现有的宇航级星载处理解决方案

随着星载数据量预计呈指数增长,我们应该使用哪种类型的处理器来进行密集型星载边缘计算?微处理器和FPGA哪个更好?欧洲航天局最近的星载数据处理研讨会探讨了当前的问题、趋势和未来的需求。

阻碍在轨边缘处理的基本技术限制是:

1.缺乏高容量、低延迟、低功耗、宇航级的存储器。目前, 高速宇航级存储器仅限于易失性的DDR3/DDR4 SDRAM。此前我解释了,实现1Tb星载存储需要64片16Gb芯片,消耗总计17瓦功率,需要152.3立方厘米物理空间和468,060英镑经济成本。这非常难以实现。另一方面,宇航级的非易失性内存速度很慢

2.缺乏为空间应用提供所需处理能力的低功耗微处理器或FPGA。在过去十年中,基于65和20纳米SRAM的FPGA提供了功耗为20瓦的有效载荷处理,而基于28纳米闪存的器件提供了更低功耗的解决方案。超深亚微米性能、逻辑密度和资源会导致功耗的增加。具有处理原始数据的性能的宇航级微处理器的功耗超过30瓦。

3.现有的宇航级微处理器或FPGA无法有效融合和处理来自多个传感器的输入。在处理器之间移动大量的信息会造成数据密集型计算的性能瓶颈。

4.现有的宇航级微处理器或FPGA无法有效地实现针对目标识别和分类的深度学习算法。

针对边缘处理的新型解决方案

对于那些需要在轨边缘星载处理的应用,最新的FPGA和微处理器正努力解决上述局限:

1.我在之前的一篇文章中介绍过小形状因数的4GB高速(高达2400MT/s)宇航级DDR4内存,并对该SDRAM的硬件设计进行了讨论。

2.低功耗的28纳米闪存FPGA降低了功耗,更节能的微处理器提高了GFlops/W值。

3.2020年以来,Teledyne e2v推出的耐辐射、QLS1046-4GB计算密集型微处理器引入了数据路径加速架构(DPAA), 以提高数据包解析、队列管理、硬件缓冲区管理和加密,支持IEEE 1588精确时间协议。自2020年以来,Xilinx的XQRKU060也改善了信息流和吞吐量,优化了数据路径、I/O和内存接口以降低延迟。

4.新一代7纳米FPGA包含专门用于处理线性代数的人工智能芯片,以提高深度学习算法的性能。QLS1046-4GB包含四个核心,每个核心都集成了本地矢量协处理器e.NEON。

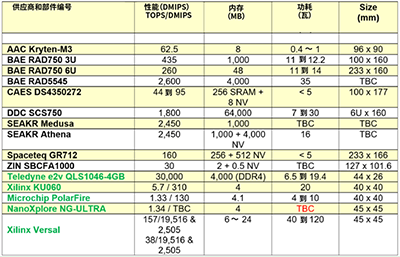

表2包含最新的宇航级FPGA和微处理器:前者结合了可配置逻辑和微处理器,新一代的器件将集成用于高效矢量处理的人工智能芯片。对于以绿色显示的FPGAs/MPSoCs,标称的性能是基于资源数和时钟频率的理论峰值。实际的计算水平将会更低,这取决于其使用和实现方式、内存和I/O使用情况。表2提供了包括软核、RISC CPU在内的有用的比较信息。KU060和Versal器件的高度并行特性反映在它们较大的TOPS值上。

表2 宇航级星载处理解决方案的比较

随着星载数据量的显著增加,使用人工智能和机器学习技术,为时间关键型和非实时型应用进行在轨分析的自主有效载荷处理呈现出增长趋势。例如,一个在地面站覆盖范围之外的空间碎片回收航天器无法收到迟来的避免碰撞的指令。从多个传感器获取的星载态势感知加上随后的目标检测和分类,将使这种时间关键决策能够在不受人类干预的情况下实时做出。类似地,高分辨率SAR图像会产生大量的地球观测数据,在轨人工智能推理和神经网络技术将允许特征识别、场景分割和特征描述,而不是阻塞宝贵的RF下行链路。

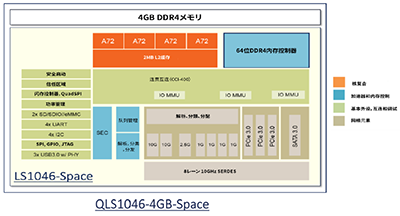

Teledyne e2v推出耐辐射的Qormino QLS1046-4GB四核处理器,包含4个ARM® Cortex® A72核(最高运行频率为1.8GHz) 和4GB高速DDR4 SDRAM,形状因数为44x26毫米,如下图所示。它将CPU和片外存储器集成到单个基板上,无需设计复杂耗时的接口,并具有显著的尺寸、重量和功率(SWaP)优势,可用于在轨边缘处理。该器件的计算性能为30000 DMIPS或超过45000 CoreMarks。

四个MPU包含ARMv8-A架构,每个都有自己的一级32KB数据缓存和48KB指令缓存,并共享一个公共的2 MB二级缓存,如图2所示。在核心频率为1.2GHz,供电电压为1伏,DDR速率为1.6GT/s时, QLS1046-4GB的总功耗范围为6.5到12瓦(不含外围设备),具体取决于允许的最大结温。在1.8GHz,供电为1伏,DDR4速率为2.1GT/s时,器件的功耗为9.3到19.4瓦。QLS1046-4GB的卓越计算性能和可以突破I/O瓶颈限制的内存带宽,以及较小的形状因数,使其与表1中列出的解决方案相比更加优秀。

图1 Qormino® QLS1046A-4GB处理器和内存[Teledyne e2v]

图2 Qormino® QLS1046A-4GB方框图

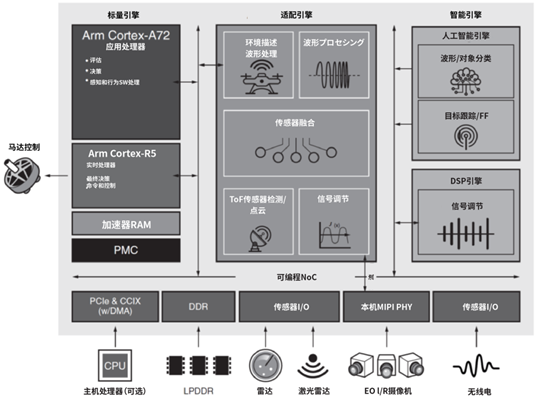

去年9月,Xilinx宣布将发布其Versal ACAP(自适应计算加速平台)的耐辐射版本。该器件包含一个由VLIW SIMD 高性能核心组成的人工智能引擎阵列,包含用于固定和浮点操作的矢量处理器、标量处理器、专用程序和数据内存、 专用AXI通道并支持DMA和锁定。

人工智能芯片提供高达6路的并行指令,包括每个时钟周期的2/3个标量操作、2个矢量读取和1个矢量写入以及1个固定或浮点矢量操作。数据级并行性是通过矢量级操作实现的,在矢量级操作中,可以在每个时钟周期的基础上操作多个数据集。与最新的FPGA和微处理器相比,人工智能引擎将机器学习算法的性能分别提高了20倍和100倍,而功耗仅为50%。与表1中列出的现有的处理解决方案相比,人工智能芯片是实现智能、自主的在轨边缘处理的关键区别性特征。

图3 Xilinx的Versal ACAP框图[Xilinx]

总结

对于正在研发的应用,哪种类型的星载处理器更好?FPGA,微处理器还是ACAP?这很大程度上取决于算法是如何实现的,例如芯片内缓存的使用、外部内存访问的数量和频率、流水线、并行化和缓冲。最新的宇航级器件性能优于商用GPU,性价比也更高。

对于高分辨率SAR视频,QLS1046-4GB的原始计算性能、高速内存接口和小形状因数,使其非常适合从地球观测成像数据中提取实时信息。高达2.1GHz的DDR4速率突破了传统的I/O瓶颈。

对于态势感知,例如识别敌我或避免空间碎片碰撞,KU060等最新的FPGA能够低延迟实时接收和处理来自多个传感器的高达Tbps的数据,从而实现ASIC级的系统级性能。对于空间原位探测和资源利用也同样如此。FPGA可以处理各种高计算要求的算法,擅长数据移动、自定义加速、面向位的函数和接口。

在目标分类、人工智能推理和自主决策方面,Xilinx的ACAP可帮助实现高效的边缘矢量计算解决方案,为碎片回收航天器或基于实时流量需求的可重构认知应答器的后期指挥提供特征识别。神经网络的实现需要TeraOPS的性能和Versal提供的特定领域的并行性。这些7纳米器件可能非常耗电,所以需在项目前期进行功耗预测,以确保它们满足功率的分配预算。QLS1046-4GB能以更低的功耗和更低的成本提供深度学习。

宇航级微处理器、FPGA和ACAP是互补的星载处理技术,各自具有独特的优势。在轨边缘处理需要对从数据源处的多个传感器获取的大量信息进行实时计算,要求低延迟的确定性接口,具有包含独特散热和可靠性要求的小型低功耗形状因数。

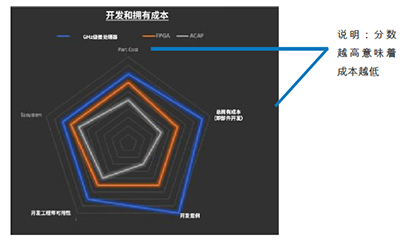

在为密集型在轨边缘计算选择最合适的星载处理器时,还需要考虑投向市场的时间、实现和采购方面的因素,例如FPGA通常需要比微处理器更多的电源,这意味着需要更多的稳压器,因此需要更大的印刷电路板来满足这些需求。FPGA还以设计难度大而著称。对于一些项目,投向市场的时间可能非常短,OEM会坚持使用来自熟悉供应商的现有设备,以加快硬件设计。一些制造商没有学习新开发工具或不同编程语言的技能或时间。最新的超深亚微米的宇航级FPGA价格高达六位数,这对许多OEM来说也是一大障碍,尤其是那些以低成本的新空间应用为目标的厂商。

新一代在轨边缘处理将结合微处理器、FPGA和智能计算,形成一个紧密集成的异构平台。这需要多种引擎类型,因为没有一种引擎能够以最佳方式执行应用所需的所有任务。标量微处理器是进行控制、复杂决策和支持操作系统的理想选择,可重新配置的FPGA增加了处理各种高要求算法的灵活性,智能引擎则为机器学习和AI推理优化了线性代数和矢量算法的计算。

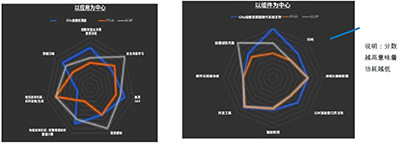

以下雷达图(图4)比较了QLS1046-4GB、最新的超深亚微米宇航级FPGA和在轨边缘处理ACAP:

图4 星载处理解决方案的比较

(作者:Rajan Bedi)